- 全部

- 默认排序

安装的电路设计软件是Cadence Allegro16.6,在使用过程中发现软件不能加载使用的现象,大家有没有发现这种现象和解决的办法?以上是安装包文件昨天安装好软件后可以正常使用,可是今天早上在使用的时候发现在原理图的时候报错PCB也是有问题环境变量设置如下请问大家在使用过程中出现过这种报错吗,是

为什么我安装的Cadence Allegro SPB OrCAD 16.6 没有capture cis的功能我想关联一下数据库用

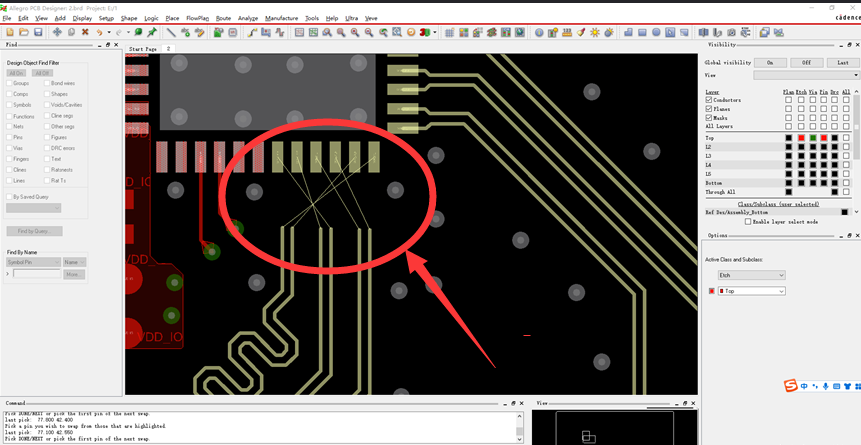

很多电子初学者在使用Cadence Allegro进行Layout设计时,会有一些mipi或lvds等差分走线,在走线时可能为了匹配线序,导致信号网络的走线是交叉,这样做不仅费时费力,还会影响信号质量,那么如何将这些器件的引脚交换过来?如图

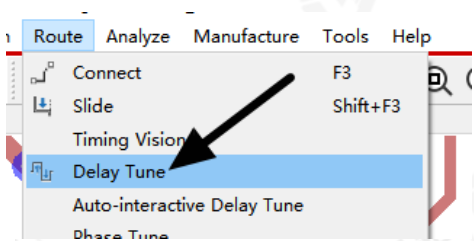

在PCB设计中做等长时,常常会用到蛇形走线,下面就介绍一下如何进行蛇形走线及相关设置:执行菜单面临Route-Delay Tune,在Options进行相关设置,其中Style是蛇形等长的样式,Gap一般设置为3倍线宽,Corners角度一

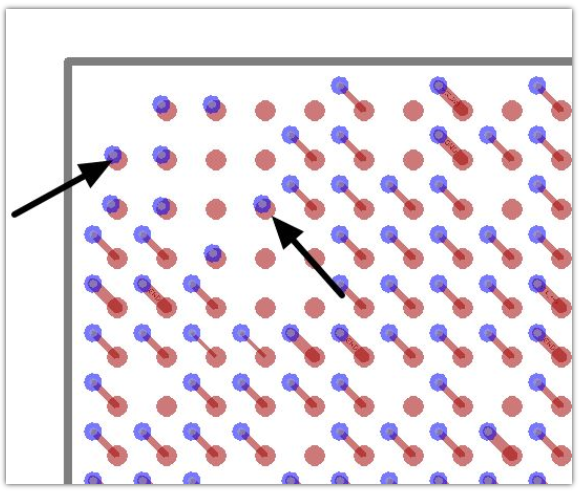

对于BGA扇孔,同样过孔不宜打孔在焊盘上,推荐打孔在两个焊盘的中间位置。很多工程师为了出线方便,随意挪动BGA里面过孔的位置,甚至打在焊盘上面,如图1所示,从而造成BGA区域过孔不规则,易造成后期焊接虚焊的问题,同时可能破坏平面完整性。图1

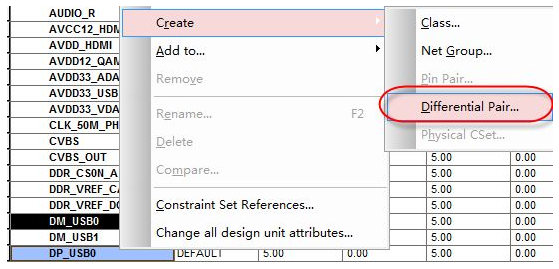

设计PCB过程中,若设计中有差分对信号,则需要将是差分的2个信号设置为差分对,设置差分对有2种方式:手动添加及自动添加一、手动添加差分对:1、点击Setup-Constraints-Constraint Manager调出CM规则管理器,然

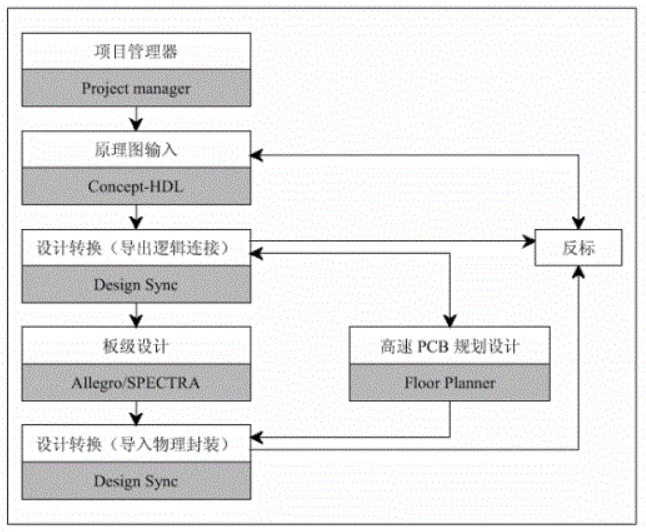

随着时代发展,EDA工具越来越多种,市场上的主流EDA软件大致上可归类为Altium Designer、Cadence Allegro、Metro Pads,也是现在的电子工程师必须重点了解的工具之三,今天我们来聊聊基于Allegro根据的

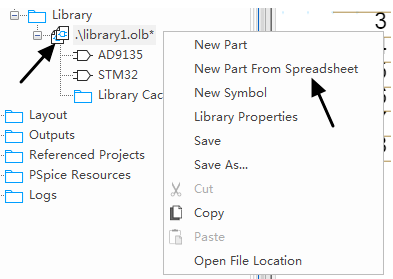

在我们遇到引脚数量特别多的芯片时,此前用的创建元件的方法会显得特别的麻烦,且费时费力,也会容易出现错误,这时我们可以通过Capture导入Excel表格的方式来方创建元件。第一步,右击.olb文件,点选New Part From Sprea

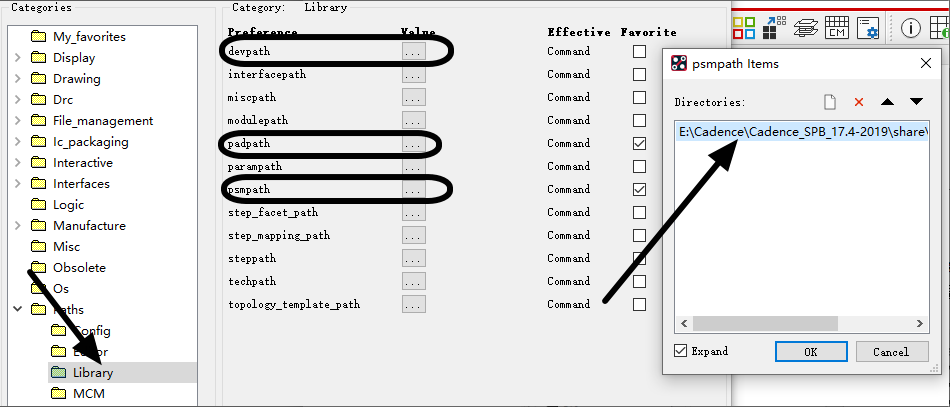

打开Allegro软件,执行菜单命令Setup-User Preferences,在如图所示的用户参数窗口进行库路径的指定,对debpath,padpath及psmpath库进行所需要调用封装库所在路径的指定,这样就可以调用本地的pcb封装

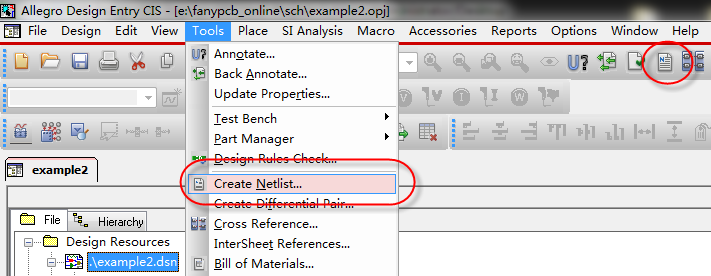

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

扫码关注

扫码关注